综合报错

报错:[Common 17-69] Command failed: Vivado Synthesis failed

[Synth 8-5535] port has illegal connections. It is illegal to have a port connected to an input buffer and other components. The following are the port connections :

Input Buffer:

Port I of instance clkin1_ibufg(IBUF) in module

Other Components:

Port CLKIN1 of instance \u_mig_7series_0_mig/u_ddr3_infrastructure/plle2_i (PLLE2_ADV) in module mig_7series_0

[Synth 8-2918] Failing due to illegal port connections

解答:这是一个关于时钟连接冲突的经典综合错误。问题在于同一个时钟端口 sys_clk 被同时连接到了两个不同的时钟管理组件,这在FPGA设计中是不允许的,这违反了"一个时钟源只能驱动一个时钟管理单元"的规则

订正:让 clk_wiz_1 为 MIG 提供时钟。

module top_cx(

input wire sys_clk, // 系统时钟输入

// ... 其他端口

);

// 时钟向导实例

clk_wiz_1 clk_wiz_1_inst (

.clk_in1(sys_clk), // 主时钟输入

.clk_out1(clk_100m), // 100MHz 系统时钟

.clk_out2(clk_200m), // 200MHz 给MIG的时钟

.clk_out3(clk_other), // 其他需要的时钟

.reset(1'b0),

.locked(clk_locked)

);

// MIG DDR3控制器实例

mig_7series_0 mig_7series_0_inst (

.sys_clk_i(clk_200m), // 使用时钟向导输出的时钟

.clk_ref_i(clk_200m), // 参考时钟

// ... 其他MIG连接

.sys_rst(!clk_locked) // 时钟未锁定时复位

);

//......

endmodule

编译报错: implementaion complete,failed timing & nets

解答:当 Vivado 实现完成但出现时序违规和网表问题时,这表明您的设计虽然在逻辑上正确,但无法在目标 FPGA 上以要求的速度稳定运行。这是一个非常常见且关键的阶段。

订正步骤:

1)检查约束

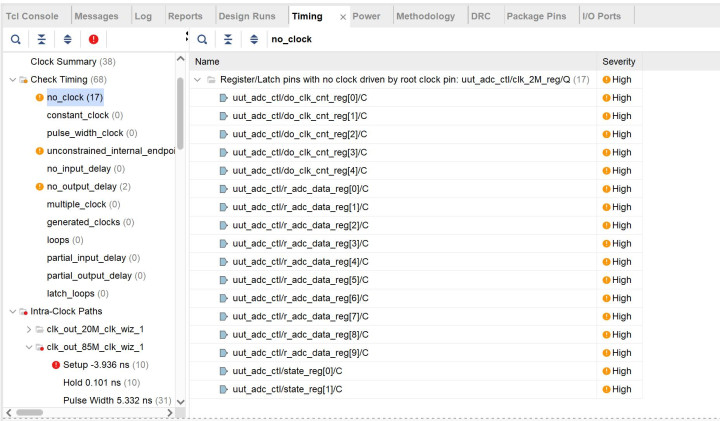

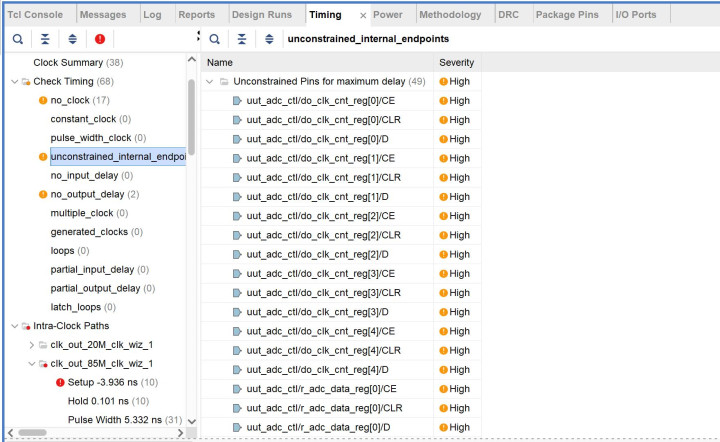

通过TCL命令checking_timing检查约束。

check_timing -name mycheck

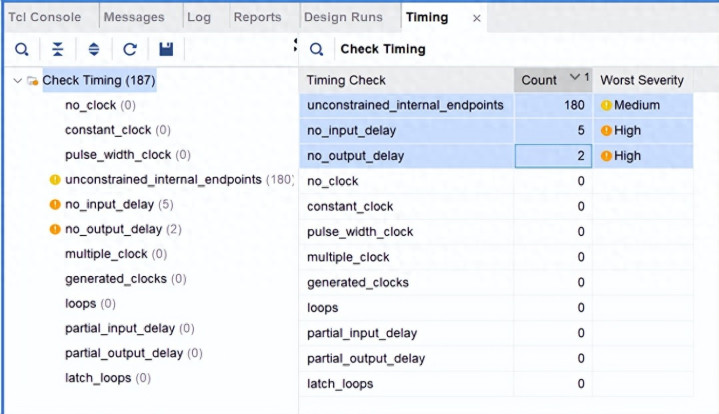

显示如下:

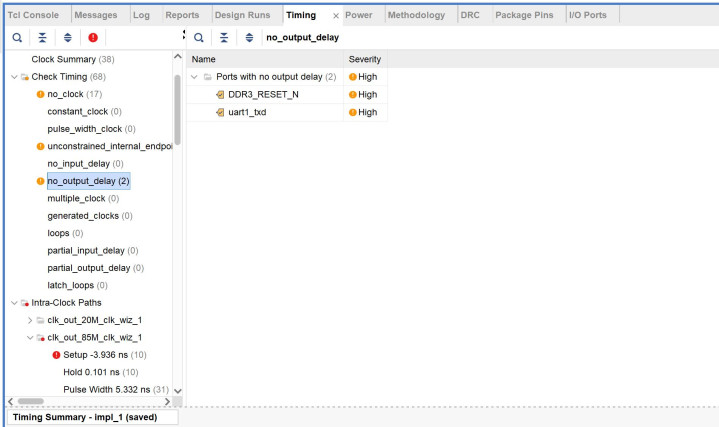

报告说明:no_input_delay和no_output_delay严重程度较高。unconstrained_internal_endpoints严重程度中等

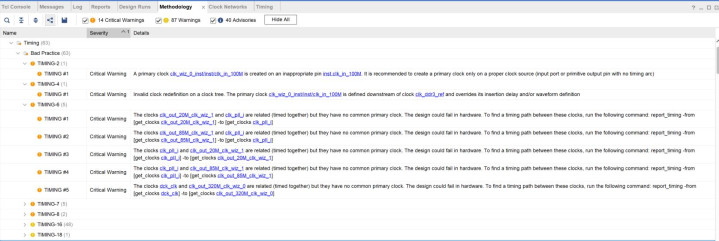

通过TCL命令report_methodology检查约束

该报告会生成UFDM报告,该报告包含了TIMING和XDC条目,会显示在时序约束方面的不规范设计,尤其是其中Bad practice部分。

通过TCL命令report_clock_networks检查时钟周期约束。

report_clock_networks -name myclknet

打开 Implementation 后的设计。

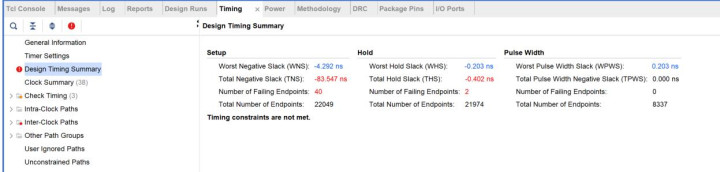

在 Reports 标签页下,找到 Timing 部分,打开 Timing Summary 报告。

重点关注:

WNS: 最差负时序裕量。如果为负,说明有建立时间违规。

WHS: 最差保持时间裕量。如果为负,说明有保持时间违规。

TNS: 总负时序裕量。所有违规路径的裕量之和,反映了问题的严重程度。

违规路径数量: 看看是少数几条关键路径有问题,还是大面积违规。

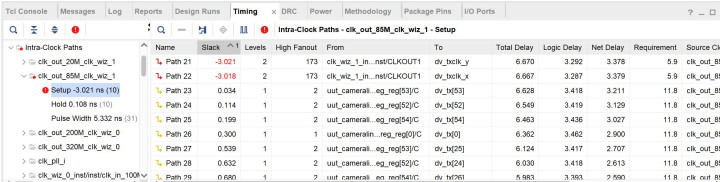

违例路径1:from clock: clk_wiz_1_inst/inst/mmcm_adv_inst/CLKOUT1,to clock: dv_txclk_y,时钟违例setup -3.021ns。

时序报告关键信息解读表格

报告字段

含义

对板级延迟的启示

Slack

时序违例

实际延迟 > 约束延迟

Slack > 0

时序满足

可能有优化空间

Data Arrival Time

数据实际到达时间

反映真实延迟

Clock Arrival Time

时钟到达时间

影响时序分析基准

Clock Skew

时钟路径偏斜

增加有效的数据有效窗口变化

Uncertainty

时钟不确定性

需要预留的裕量,总时序裕量 = 周期 - (逻辑延迟 + 布线延迟 + 板级延迟 + 不确定性)

这个时序违例是从clk_wiz_1_inst/inst/mmcm_adv_inst/CLKOUT1到dv_txclk_y的路径。违例值为-3.021ns,即建立时间不满足要求。

根据slack报告,要求的时间是8.074ns,而实际到达的时间是11.096ns,这意味着数据到达太晚,超过了时钟周期允许的时间。

同时,我们注意到时钟延迟:

Destination Clock Delay (DCD): -1.370ns

Source Clock Delay (SCD): -1.457ns

Clock Pessimism Removal (CPR): -0.087ns

从这些数据可以看出,时钟路径上的延迟较大,且目的时钟延迟(DCD)和源时钟延迟(SCD)都为负值,这通常表示时钟在布线中遇到了较长的路径。

可能的原因和解决方法:

1)检查这两个时钟的周期和关系。如果这两个时钟是同步的,那么可能需要调整多周期路径约束或调整时钟不确定性。

2)如果这两个时钟是异步的,那么应该设置set_clock_groups将这两个时钟设为异步,这样就不会检查它们之间的时序。

3)如果这两个时钟是同步的,但是数据路径太长,导致延迟过大,那么需要优化数据路径。

我们已经为这两个时钟域添加了多周期路径约束和时钟不确定性约束,但违例仍然存在。现在我们需要考虑其他方法。

可能的解决方案:

1)进一步增加多周期路径的周期数,因为当前设置的多周期路径为2可能还不够。

2)检查是否可以将这些路径设置为虚假路径(false path),如果它们确实是异步的。

3)优化设计,减少数据路径的延迟。

4)调整时钟约束,例如增加时钟不确定性,或者调整时钟延迟。

2)分析具体的违规路径

在 Timing Summary 报告中,点击 Check Timing 链接,会列出所有失败的路径。

双击一条失败的路径,Vivado 会打开 Timing Path 报告窗口,以图形化和文本方式展示整条路径。

分析路径报告的关键信息:

起点和终点: 路径是从哪个寄存器开始,到哪个寄存器结束。

逻辑级数: 路径上经过了多少个 LUT 和其他的逻辑单元。级数越多,延迟越大。

关键网络: 是哪根线的延迟特别长?

时序模型: 查看建立时间要求和路径的实际延迟是如何计算的。

3)检查网表问题

“Nets” 问题通常指 布线拥塞 或 无法布通。

在 Reports -> Route Design 下查看 Route Status 报告。如果显示的不是 “Fully Routed”,说明有布线问题。

在图形化界面中,选择 Layout -> Routing -> Congestion 查看布线拥塞热力图。红色和黄色区域表示拥塞严重,是问题的焦点。

步骤:1)先运行 report_route_status 和 report_drc 确定问题范围;2)检查拥塞报告,如果是拥塞问题,调整布局策略;3)检查时序报告,如果是时序问题,优化约束;4)检查高扇出网络,添加适当的约束;5)最后考虑修改设计或添加物理约束。

以下是对约束代码的意见和建议:

1)时钟定义:

主时钟定义正确,但需要注意是否所有输入时钟都已定义。

生成时钟的定义需要确保源时钟正确,并且路径存在。

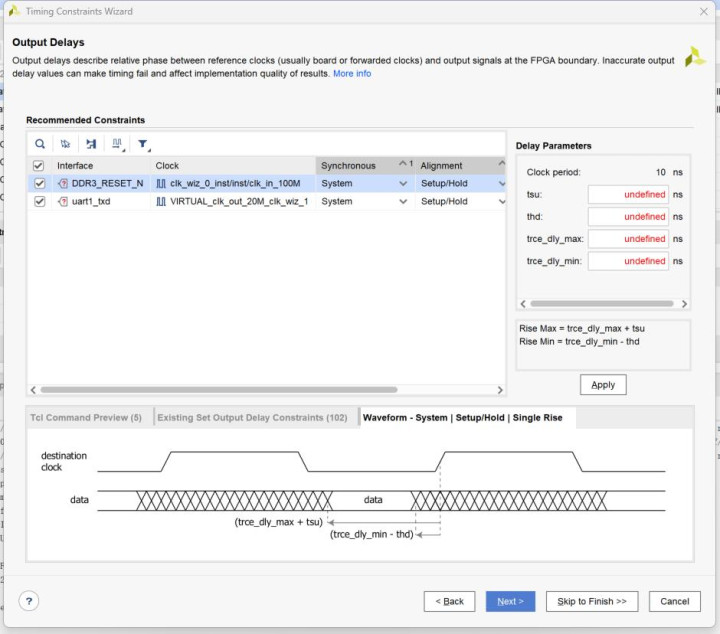

2)输入/输出延迟约束:

需要确保所有输入/输出端口都有正确的时钟参考。

检查是否有遗漏的端口未约束。

输入延迟Input Delay - 告诉 FPGA 外部数据何时到达

要回答的问题:“相对于我的 FPGA 输入时钟,外部芯片发送的数据是什么时候到达我的 FPGA 引脚的?”

这个时间由两部分组成:外部芯片的时钟到输出延迟(Tco),PCB 板上的走线延迟(Flight Time)。

计算公式:Max Input Delay = Tco_max + PCB_delay_max用于建立时间检查。这是数据可能到达的最晚时间。

Min Input Delay = Tco_min + PCB_delay_min用于保持时间检查。这是数据可能到达的最早时间。

“Delay Parameters”(延迟参数)是约束 I/O 时序的核心,它直接关系到你的 FPGA 与外部芯片(如 DDR、ADC、DAC、其他处理器等)能否正确通信。

这些参数的本质是描述 FPGA 外部信号的时序关系。Vivado 工具需要知道这些信息,才能在布局布线时,优化 FPGA 内部的逻辑和路径,确保信号在到达 FPGA 引脚时能满足外部器件的建立和保持时间要求。

核心概念:系统同步 vs 源同步

在填写之前,你必须先确定你的接口是哪种类型,因为计算方法完全不同。

系统同步

特点:FPGA 和外部芯片共享同一个系统时钟源。数据和时钟是分离的。

典型应用:传统的并行总线、异步 SRAM、一些简单的 ADC/DAC。

时序分析模型:基于公共时钟的建立/保持时间分析。

源同步

特点:数据发送方(Source)在发送数据的同时,也发送一个随路的时钟或选通信号(如 DQS)。数据和时钟是同步传输的,对板级走线延迟不敏感。

典型应用:DDR SDRAM、MIPI、Camera Link、千兆以太网(RGMII)、高速 ADC/DAC。

时序分析模型:基于随路时钟的建立/保持时间分析。

绝大多数现代高速接口都是源同步的。

输出延迟Output Delay- 表示数据在时钟边沿之后多长时间内必须稳定(从芯片外部看)。所以,输出延迟值越大,说明数据需要更早地到达端口,即要求时间更早。

因此,增加输出延迟约束会使要求时间提前,从而使得时序更难以满足。

Tco:在外部器件的数据手册的 AC Timing Characteristics 部分查找,通常是 t_{CO} 或 CLK-to-Output 参数。

PCB Delay:通过你的 PCB 设计工具(如 Altium, Cadence)仿真得到,或者根据走线长度和介质参数估算。通常非常小(皮秒到几百皮秒量级)。

3)时钟不确定性:

设置的时钟不确定性值需要合理,过小可能导致时序难以满足,过大则可能隐藏问题。

4)多周期路径和虚假路径:

确保所有跨时钟域路径都已正确约束(多周期路径或虚假路径)。

检查是否有不必要的多周期路径约束。

5)时钟分组:

确保异步时钟组设置正确,避免不必要的时序分析。

6)物理约束:

检查是否有需要添加的物理约束,如IO标准、位置约束等。

7)其他约束:

检查是否有重复约束或冲突约束。

DDR3时序约束

根据DDR3手册确定以下参数:

1)确定DDR3的时钟频率和数据速率。

根据手册,最高数据传输速率可达1866Mbps,那么时钟频率为933 MHz(因为DDR是双倍数据速率)。

我们的参考时钟是100 MHz,通过PLL倍频到933 MHz。

2)输出延迟计算(FPGA输出到DDR3):

对于输出,我们需要确保在DDR3的DQS的上升沿和下降沿,数据满足建立和保持时间。

建立时间要求:数据必须在DQS触发沿之前至少tDS时间稳定。

保持时间要求:数据必须在DQS触发沿之后至少tDH时间保持稳定。

因此,输出延迟(set_output_delay)应该包括:

最大输出延迟(对于建立时间检查):考虑最坏情况下,数据从FPGA输出到DDR3的延迟,以及DDR3的建立时间要求。

最小输出延迟(对于保持时间检查):考虑最好情况下,数据从FPGA输出到DDR3的延迟,以及DDR3的保持时间要求。

但是,我们现有的约束中,输出延迟是相对于oserdes_clk的,而且设置的值是1.5 ns(max)和1.0 ns(min)。这些值可能是根据板级延迟和DDR3的时序要求估算的。

根据手册,tDS(AC135)为68 ps,tDH(DC160)为70 ps。这些值很小,所以我们的输出延迟应该主要考虑板级延迟和时钟偏移。

4)输入延迟计算(DDR3输出到FPGA):

对于输入,我们需要确保在FPGA的捕获时钟(可能是DQS)的沿上,数据满足建立和保持时间。

同样,输入延迟(set_input_delay)应该包括:

最大输入延迟(对于建立时间检查):考虑DDR3输出数据到FPGA的最大延迟,以及FPGA的建立时间要求。

最小输入延迟(对于保持时间检查):考虑DDR3输出数据到FPGA的最小延迟,以及FPGA的保持时间要求。

手册中给出了DQS到DQ的偏斜(tDQSQ)最大为85 ps,以及DQ输出保持时间从DQS(tQH)为0.38 tCK。

在FPGA侧,我们使用DQS来捕获数据,因此输入延迟应该相对于DQS时钟。

但是,在我们的约束中,输入延迟是相对于oserdes_clk的,而且我们没有为DDR3的读数据设置输入延迟?实际上,我们可能使用的是DDR3控制器,它内部会处理读数据的同步,因此可能不需要在约束中显式设置输入延迟。

5)时钟不确定性:

我们需要为DDR3时钟添加不确定性,包括时钟抖动和偏移。

手册中给出了时钟周期抖动(DLL锁定)为±60 ps,周期间抖动为120 ps。

因此,我们可以设置时钟不确定性为0.120 ns(最大值)。

现有约束中,我们已经为mem_refclk等时钟设置了0.15 ns的不确定性,这可能是合理的。

6)多周期路径和时钟分组:

我们已经有了一些多周期路径和时钟分组的约束,这些可能需要根据设计调整